ISSN No.: 2454- 2024 (online)

International Journal of Technical Research & Science

# A NOVEL DESIGN OF REVERSIBLE 2:4 & 3:8 DECODER

Sonam<sup>1</sup>, Ankush<sup>2</sup>

Email Id: <sup>1</sup>sonam.mongia8@gmail.com, <sup>2</sup>amongia9@gmail.com <sup>1</sup>M.C.A Department of Computers, Kurukshetra University, Kurukshetra, Haryana (India) <sup>2</sup>M.Tech, Department of ECE, Punjabi University, Patiala, Punjab (India)

**Abstract:** Decoders are one of the most important circuits used in combinational logic. Different approaches have been proposed for their design. In this paper, a 2:4 decoder & have used it to build a 3:8 decoder has been designed to reduce power consumption, delay and quantum cost using reversible technology, which is then analyzed and comparative study has been done in account of the power consumption, delay, quantum cost and memory usage. Reversible logic is used to reduce the power dissipation that occurs in digital circuits by preventing the loss of information. The proposed 2:4 & 3:8 Decoders using reversible technology gives better results in terms of reversible parameters as compare to existing results. The decoder circuits are simulated using Xilinx ISE Simulator 14.4.

Keywords: Low power, Reversible logic, MFRG gate, 2:4 Decoder; Delay.

#### 1. INTRODUCTION

Landauer [1] showed that the heat generated during computation is not due to the processing of bits, but due to the loss of information. Wiping of each bit of information causes a kTln2 amount of heat dissipation where k is the Boltzmann constant = 1.3805 \* 10^23 J/K and T is the temperature in absolute scale. While this heat may be negligible for a single wipe of information, in modern VLSI design, where many chips are arranged in small region and millions of instructions are processed per second, the information loss and consequently the heat generation is formidable.

Bennett [2] later showed that this heat dissipation can be avoided by using reversible computation. This proof by Bennett has led to an extensive research on reversible logic. Most prominent applications of reversible logic are seen in quantum computation, low power CMOS design, nanotechnology and DNA computing.

Quantum networks are composed of quantum logic gates each gate performing an elementary unitary operation on one, two or more than two state quantum systems called qubits. Each qubit represents an elementary unit of information corresponding to the classical bit values 0 and 1. Any unitary operation is reversible and hence quantum arithmetic must be built from reversible logic components [3].

Quantum cost, delay and power consumption are the most important cost metrics of reversible computing. Number

Quantum cost, delay and power consumption are the most important cost metrics of reversible computing. Number of gates is not a good measure of cost, since more than one gates can be taken together to form a new gate, thus reducing the gate count. Quantum gates involving many qubits are extremely difficult to build. Hence quantum cost is an important metric to build quantum gates. Quantum cost is the number of elementary quantum gates required to build the gate. 1\*1 reversible gates viz. NOT gate have quantum cost 0 while 2\*2 gates viz. Controlled-V, Controlled-V+, CNOT gate etc. have quantum cost 1 [4].

Design of combinational sequential circuits have been ongoing for some time. Various proposals are given for the design of adders, subtractions [5], multiplexers [6], decoders etc. Recently a new reversible SG gate [7]. In this paper, we have proposed a novel design of 2:4 decoder whose quantum cost is less than the previous design. A design has also been proposed to extend the 2:4 decoder to higher dimension i.e. 3:8 decoder using MFRG gate.

Rest of the paper is organized in the following way: Section 2 gives a brief introduction to the reversible gates used in this paper. In section 3 we give our proposed design of decoder, in section 4 the layout design of proposed decoders are discussed, in section 5 compare analysis of proposed decoders with the previous design is given. Section 6 concludes the paper.

# 2. BASIC REVERSIBLE GATES

Reversible gates are n\*n logic gates where the input vectors I = I(i1; i2; :::; in) are mapped to the output vectors O = O(o1; o2; :::; on). The mapping is bijective, i.e., every input is mapped to an output and every output has a unique input mapped to it. Thus the outputs of reversible gates are permutations of the inputs. Fan-outs are not allowed in reversible circuit since they violate one-to-one mapping. Some basic reversible gates are introduced in this section.

#### 2.1 NOT Gate

The simplest reversible gate is NOT gate. It is a 1\*1 gate with quantum cost 0. NOT gate simply flips the input as shown in Fig. 2.1.

pg. 613

www.ijtrs.com www.ijtrs.org

$$A \longrightarrow P = \overline{A}$$

Fig. 2.1 NOT Gate

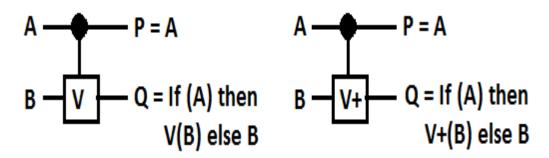

# 2.2 Controlled-V and Controlled-V+ Gate

Controlled-V and Controlled-V+ gates are 2\*2 reversible gates with quantum cost 1. In Controlled-V gate, if the control signal A=0, then the second input B passes unchanged.

Controlled-V and Controlled-V y have the following properties:

V \* V = NOT

V \* V + = V + \* V = I

V+ \* V+ = NOT

Hence Controlled-V is also called the square root of NOT gate. Quantum implementation of V and V+ are shown in Fig.2.2.

Fig. 2.2 Quantum Implementation of Controlled-V and Controlled-V+ Gate

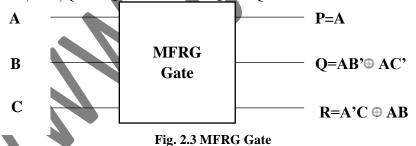

#### 2.3 MFRG Gate

Fig. 2.3 shows a 3\*3 Modified fredkin gate. The input vector is I (A, B, C) and the output vector is O (P, Q, and R). The output is defined by P=A, Q=AB'  $\oplus$  AC' and R=A'C  $\oplus$  AB. Quantum cost of a Modified fredkin gate is 4.

# 3. PROPOSED DESIGN OF DECODERS

In digital systems, instructions as well as numbers are conveyed by means of binary levels or pulse trains. A decoder is a logic circuit that converts an N-bit binary input code into M output lines such that only one output line is activated for each one of the possible combinations of inputs. The decoder identifies or recognizes or detects a particular code. The N inputs can be a 0 or a 1, there are 2N possible input combinations or codes. For each of input combination only one of the M outputs will be active (HIGH), all other outputs will remain inactive (LOW). Some decoders are designed to produce active LOW output, while all the other outputs remain HIGH.

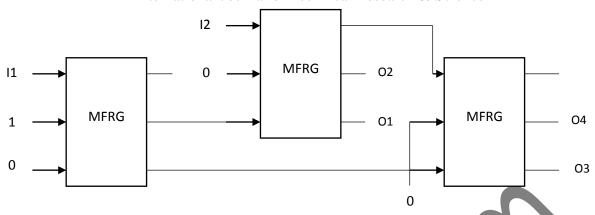

#### 3.1 2:4 Decoder

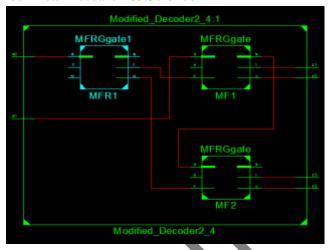

A design of 2:4 decoder using 3 Modified Fredkin gates is shown below. If x and y are the inputs to the decoder, then the four outputs will be xy, x'y, xy' and x'y'. The number of garbage output in this architecture is 1 and the number of constant inputs are 4. The existing 2:4 decoder was designed by the FRG reversible gates having quantum cost 5. The author proposed the 2:4 decoder using MFRG gate with low quantum cost of 4. The following figure shows the architecture of 2:4 decoder

pg. 614

www.ijtrs.com www.ijtrs.org

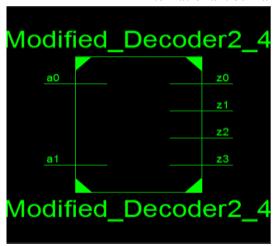

Fig. 3.1 Proposed 2:4 Reversible Decoder

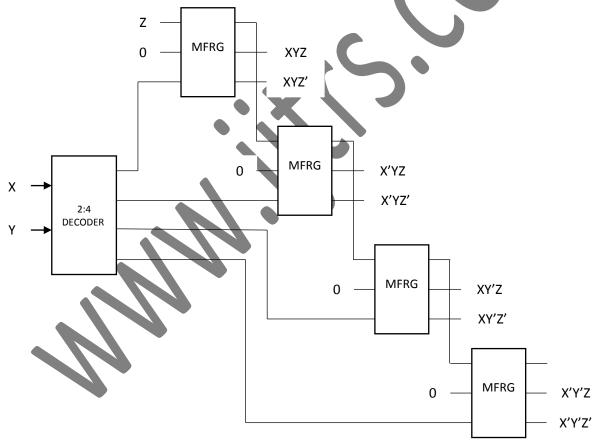

#### 3.2 3:8 Decoder

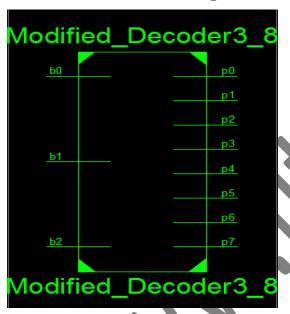

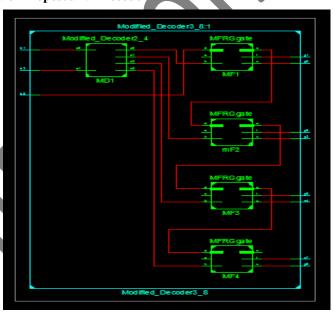

Henceforth, we shall call the 2:4 decoder as decoder block having two inputs and four outputs. A 3:8 decoder has the outputs x'y'z'; x'yz; xyz'; xyz'; xyz'; xyz; xyz'; xyz. So every output of the 2:4 decoder needs to be multiplied twice, once with z0 and then with z.

Fig. 3.2 Proposed 3:8 Reversible Decoder

A better model will be to use Modified Fredkin gate for higher dimension. Each Modified Fredkin gate is capable of performing two multiplications thus reducing the number of gates to 4 and garbage outputs to 1. The architecture is shown in Fig. 3.2.

# 4. LAYOUT SIMULATION

In this section, performance analysis of decoder has been presented. Designs simulations are done using Xilinx ISE 14.4 tool. The figure 4.1 & 4.2 shows the RTL views of various decoders

pg. 615

www.ijtrs.com www.ijtrs.org

Fig. 4.1 RTL View of Proposed 2:4 Decoder

Fig. 4.2 RTL View of Proposed 3:8 Decoder

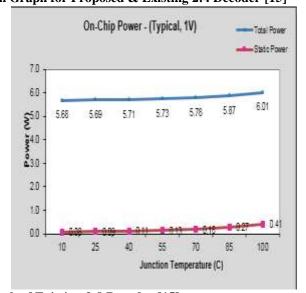

Fig. 4.3 Power Consumption Graph of Existing 2:4 Decoder [15]

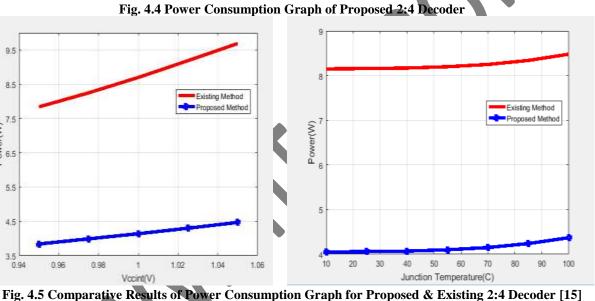

9.5 8.5 Existing Method Proposed Method 7.5 (M)Jawae 6.5 5.5 4.5 3.5 0.96 0.98 1.02 1.04 1.06 Vccint(V)

On-Chip Power over Vccint - (Typical, 87C) 6.6 6.4 6.43 62 6.15 65.8 5.6 5.4 5.88 5 63 5.39 52 5.0 48 0.95 0.975 1.025 1.05 Vecint (V)

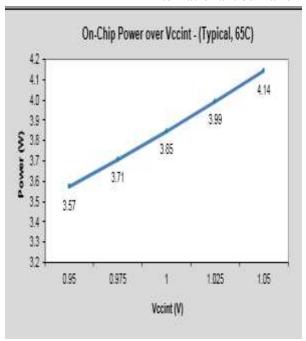

Fig. 4.6 Power Consumption Graph of Existing 3:8 Decoder [15]

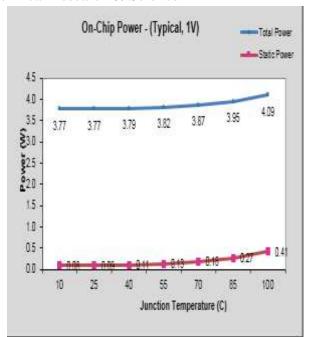

Fig. 4.7 Power Consumption Graph of Proposed 3:8 Decoder

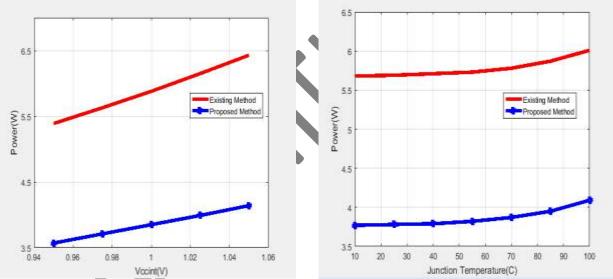

Fig. 4.8 Comparative Results of Power Consumption Graph for Proposed & Existing 3:8 Decoder [15]

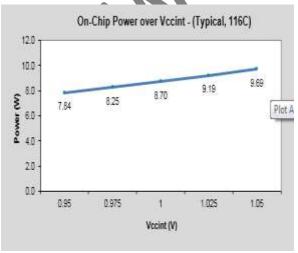

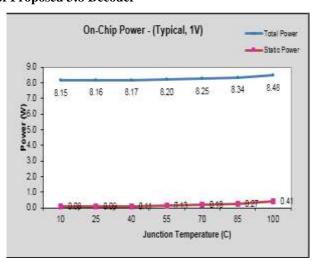

In the fig. 4.5 the graph between the Vcc and Output power shows that the propose design consumes 4.14 Watt power while the existing design consumes 8.70 Watt power. Similarly the graph between the Junction Temperature and Power shows that the propose design consumes 4.70 Watt power while the existing design consumes 8.70 Watt power.

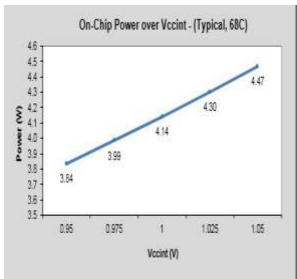

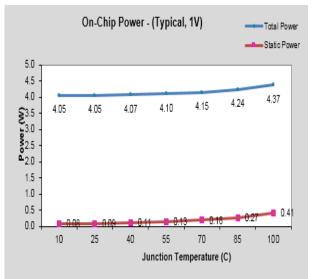

In the fig. 4.8 the graph between the Vcc and Output power shows that the propose design consumes 3.84 Watt power while the existing design consumes 5.88 Watt power. Similarly the graph between the Junction Temperature and Power shows that the propose design consumes 3.84 Watt power while the existing design consumes 5.88 Watt power.

Hence it cam be concluded that the proposed 2:4 and 3:8 decoders consumes less power as compared to the existing decoders.

#### 5. IMPLEMENTATION & RESULTS

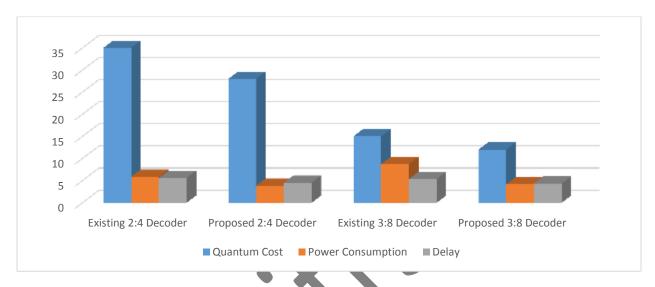

The table below gives the comparison of proposed work with the existing work in terms of quantum cost, power consumption, and delay and memory usage. We have compared our results with existing results of decoders by Ritajit Majumdar et al [15].

Table-5.1. Comparison of Proposed Work with Existing Work

| Parameters        | 2:4 Decoder     | 2:4 Decoder     | 3:8 Decoder     | 3:8 Decoder     |

|-------------------|-----------------|-----------------|-----------------|-----------------|

|                   | Existing Result | Proposed Result | Existing Result | Proposed Result |

|                   | [15]            |                 | [15]            |                 |

| Quantum Cost      | 15              | 12              | 35              | 28              |

| Power Consumption | 8.704 W         | 4.141 W         | 5.882 W         | 3.847 W         |

| _                 |                 |                 |                 |                 |

| Delay             | 5.362 ns        | 4.333 ns        | 5.607 ns        | 4.526 ns        |

| Memory            | 250876 Kb       | 240300 Kb       | 250684 Kb       | 24864 Kb        |

Fig. 5.1 Comparative Analysis for Proposed & Existing 2:4 & 3:8 Decoder [15]

The fig. 5.1 shows the comparative analysis results for quantum cost, power consumption, and delay and memory usage for various designs. The comparative results shows that our proposed designs are more efficient as compared to existing designs in terms of quantum cost, power consumption, delay and memory usage.

# **CONCLUSION**

In this article, we have proposed a novel design of 2.4 decoder and have used it to build a 3:8 decoder. The increase in the number of Fredkin gates is exponentially higher for increase in a single input. Though for n inputs, the number of outputs is 2n. Hence, from the point of view of the number of outputs, the increase in gates is linear. However, by using any other gates like Toffoli, Peres or TR gate, the number of gates will be twice as high and hence the quantum cost will be nearly twice. The number of garbage outputs also increases in the same manner since each Fredkin gate has one garbage output for this architecture. Low power consumption and quantum cost is obtained using proposed logic for designed 2:4 & 3:8 Decoder.

# REFERENCES

- [1] R. Landauer, "Irreversibility and heat generation in the computing process", IBM Journal of Research and Development, vol. 5, 1961, pp. 183-191.

- [2] C. H. Bennett, "Logical reversibility of computations", IBM Journal of Research and Development, vol. 17, 1973, pp. 525-532.

- [3] Vlatko Vedral, Adriano Bareno, Artur Ekert, "Quantum networks for elementary arithmetic operations", arXiv:quantph/9511018 v1, November 1995.

- [4] M. Mohammadi and M. Eshghi, "On figures of merit in reversible and quantum logic designs", Quantum Information Processing, 8(4):297318, Aug. 2009.

- [5] H. G. Rangaraju, U. Venugopal, K. N. Muralidhara, K. B. Raja, "Low power reversible parallel binary adder/subtractor", arXiv.org/1009.6218, 2010.

- [6] Vandana Shukla, O. P. Singh, G. R. Mishra, R. K. Tiwari, "Novel design of a 4:1 multiplexer circuit using reversible logic", International Journal of Computational Engineering Research, vol 3, issue 10, Oct 2013.

ISSN No.: 2454- 2024 (online)

### International Journal of Technical Research & Science

- [7] Payal Garg, Sandeep Saini, "A novel design of compact reversible SG gate and its applications", 2014 14th International Symposium on Communications and Information Technologies (ISCIT), Sept 2014, pages 400-403, doi: 10.1109/ISCIT.2014.7011941

- [8] R. Feynman, "Quantum mechanical computers", Optic News, vol. 11, pp. 11-20, 1985.

- [9] A. Peres, "Reversible logic and quantum computers", Phys. Rev. A, Gen. Phys., vol. 32, no. 6, pp. 32663276, Dec. 1985.

- [10] H. Thapliyal, N. Ranganathan, "A new design of the reversible subtractor circuit", doi: 10.1109/NANO.2011.6144350.

- [11] T. Toffoli, "Reversible Computing", Tech Memo MIT/LCS/TM-151, MIT Lab for Comp. Sci., 1980.

- [12] Sk Noor Mohammad, Siva Kumar Sastry Hari, Shyam Shroff, V. Kamakoti, "Constructing online testable circuits using reversible logic", VLSI-India.org, VSI pub, VDAT, 2006.

- [13] A. Kumar, S. Gugnani, "Synthesis of 4 to 16 reversible decoder", ITSI Transactions on Electrical and Electronics Engineering, 2320-8945, vol I, issue 5, 2013.

- [14] Ankush, Amandeep Singh Bhandari, "Review Paper on Reversible Logic Gate", International Journal for Research in Electronics & Communication Engineering, vol. 1, Issue 7, (2016).

- [15] Ritajit Majumdar, Sandeep Saini, '' A Novel Design of Reversible 2:4 Decoder', doi: 978-1-4799-6761-2/15/\$31.00 ©2015 IE

- [16] Ankush, Amandeep Singh Bhandari, "Design & Performance Analysis of Low Power Reversible Carry Skip Adder", IOSR Journal of VLSI and Signal Processing, vol. 6, Issue 4, Ver. II, (2016),pp.33-39

- [17] Ankush, Amandeep Singh Bhandari, "Design & Performance Analysis of Low Power Reversible Residue Adder", International Journal of Hybrid Information Technology, vol. 9, Issue 9, (2016), pp. 93-102.

- [18] Ankush, Sonam, "An Improved Design of Low Power BCD Adder using Reversible Computing", International Journal of Advance Science & Technology, vol. 104, pp.33-42, (2017).

- [19] Ankush, Sonam "Efficient Design of Low Power Multiplier using MHNG Reversible Logic Gate", International Journal of Technical Research & Science, vol. 2, Issue VIII, August 2017,pp.434-440

- [20] Ankush "Design and Implementation of Low Power Parity Preserving Carry Skip Adder Using Reversible Computing", International Journal of Advance Science & Technology, vol. 107, pp.61-72, (2017).